# Low Power Stereo ADC with PLL and TDM Interface

### **DESCRIPTION**

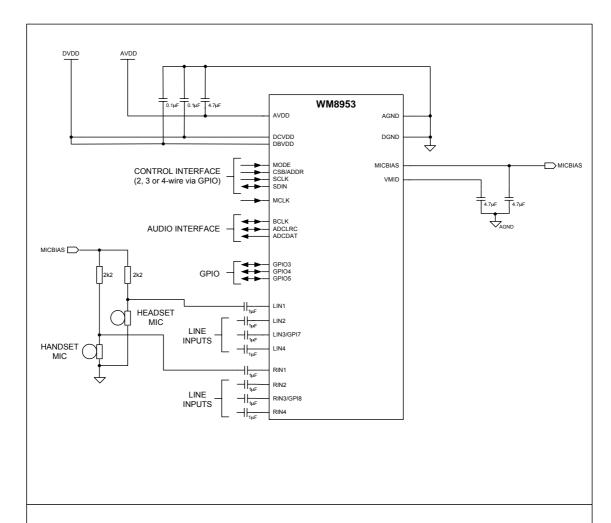

The WM8953 is a low power high performance stereo ADC designed for mobile handsets and other portable devices.

Four single-ended or differential input connections are provided, with up to 60dB of analogue gain in each input path. Stereo 24-bit sigma-delta ADCs provide hi-fi quality audio recording of microphones or line input. A programmable high pass filter is available in the ADC path for removing DC offsets and suppressing wind and other low frequency noise.

A low noise microphone bias with programmable current detect and short-circuit detect is provided.

A flexible digital audio interface supports most commonly-used clocking schemes. The audio interface supports TDM and tristate outputs allow multiple devices to share the same interface.

An integrated low power PLL provides support for most commonly-used audio sample rates.

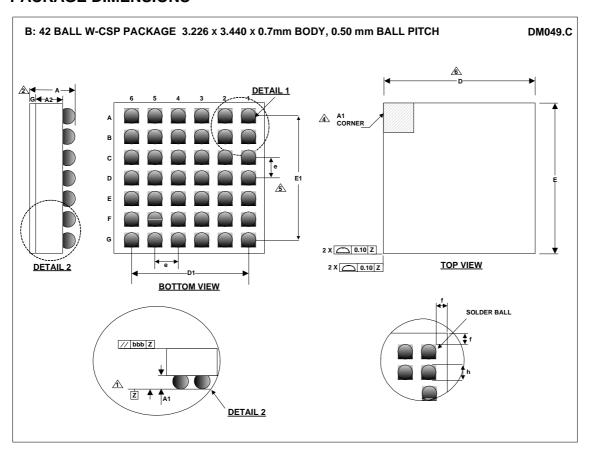

The WM8953 is supplied in very small and thin 42-ball WCSP package, ideal for portable systems.

### **FEATURES**

- SNR 94dB ('A' weighted)

- THD -82dB at 48kHz, 3.3V

- Full stereo microphone / line input interface

- Low noise MICBIAS

- Low power consumption

- Full analogue and digital volume control

- PLL provides flexible clocking scheme

- 2-wire, 3-wire or 4-wire control

- Sample rates: 8, 11.025, 12, 16, 22.05, 24, 32, 44.1, 48kHz

- · GPIO functions available

- Digital supply: 1.71V 3.6V

- Analogue supply: 2.7V 3.6V

- W-CSP package (3.226 x 3.44 x 0.7mm, 0.5mm pitch)

### **APPLICATIONS**

- Multimedia phones

- General purpose low power audio ADC

# **TABLE OF CONTENTS**

| FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

| APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

| PIN CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

| PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

| RECOMMENDED OPERATING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

| THERMAL PERFORMANCE                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

| TERMINOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |

| TYPICAL POWER CONSUMPTION                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13                                                                         |

| PSRR PERFORMANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

| AUDIO SIGNAL PATHS                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

| SIGNAL TIMING REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

| SYSTEM CLOCK TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| AUDIO INTERFACE TIMING – MASTER MODE                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

| AUDIO INTERFACE TIMING - SLAVE MODE                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| AUDIO INTERFACE TIMING – TDM MODE                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| CONTROL INTERFACE TIMING – 2-WIRE MODE                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

| CONTROL INTERFACE TIMING – 3-WIRE MODE                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

| CONTROL INTERFACE TIMING – 4-WIRE MODE                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

| INTERNAL POWER ON RESET CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

| DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.0                                                                        |

| INPUT SIGNAL PATH                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| INPUT SIGNAL PATHANALOGUE TO DIGITAL CONVERTER (ADC)                                                                                                                                                                                                                                                                                                                                                                                                             | 36                                                                         |

| INPUT SIGNAL PATHANALOGUE TO DIGITAL CONVERTER (ADC)DIGITAL AUDIO PATHS                                                                                                                                                                                                                                                                                                                                                                                          | 36<br>39                                                                   |

| INPUT SIGNAL PATHANALOGUE TO DIGITAL CONVERTER (ADC)DIGITAL AUDIO PATHSTHERMAL SENSING                                                                                                                                                                                                                                                                                                                                                                           | 36<br>39<br>40                                                             |

| INPUT SIGNAL PATHANALOGUE TO DIGITAL CONVERTER (ADC)DIGITAL AUDIO PATHSTHERMAL SENSINGGENERAL PURPOSE INPUT/OUTPUT                                                                                                                                                                                                                                                                                                                                               |                                                                            |

| INPUT SIGNAL PATH                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| INPUT SIGNAL PATH                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| INPUT SIGNAL PATH ANALOGUE TO DIGITAL CONVERTER (ADC) DIGITAL AUDIO PATHS THERMAL SENSING GENERAL PURPOSE INPUT/OUTPUT DIGITAL AUDIO INTERFACE DIGITAL AUDIO INTERFACE CONTROL CLOCKING AND SAMPLE RATES. CONTROL INTERFACE                                                                                                                                                                                                                                      | 36<br>39<br>40<br>41<br>56<br>63<br>67                                     |

| INPUT SIGNAL PATH                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36<br>39<br>40<br>41<br>56<br>63<br>75                                     |

| INPUT SIGNAL PATH                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36<br>39<br>40<br>41<br>56<br>67<br>75<br>79                               |

| INPUT SIGNAL PATH                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36<br>39<br>40<br>41<br>56<br>63<br>75<br>75                               |

| INPUT SIGNAL PATH ANALOGUE TO DIGITAL CONVERTER (ADC) DIGITAL AUDIO PATHS THERMAL SENSING GENERAL PURPOSE INPUT/OUTPUT DIGITAL AUDIO INTERFACE DIGITAL AUDIO INTERFACE CONTROL. CLOCKING AND SAMPLE RATES. CONTROL INTERFACE POWER MANAGEMENT POWER DOMAINS REGISTER MAP REGISTER BITS BY ADDRESS                                                                                                                                                                | 36<br>39<br>40<br>41<br>56<br>63<br>75<br>75<br>82                         |

| INPUT SIGNAL PATH                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36<br>39<br>40<br>41<br>56<br>63<br>75<br>75<br>82<br>82                   |

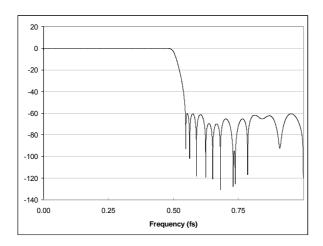

| INPUT SIGNAL PATH ANALOGUE TO DIGITAL CONVERTER (ADC) DIGITAL AUDIO PATHS THERMAL SENSING GENERAL PURPOSE INPUT/OUTPUT DIGITAL AUDIO INTERFACE DIGITAL AUDIO INTERFACE CONTROL CLOCKING AND SAMPLE RATES CONTROL INTERFACE POWER MANAGEMENT POWER DOMAINS REGISTER MAP REGISTER BITS BY ADDRESS DIGITAL FILTER CHARACTERISTICS ADC FILTER RESPONSES                                                                                                              | 36<br>39<br>40<br>41<br>56<br>63<br>75<br>75<br>82<br>82                   |

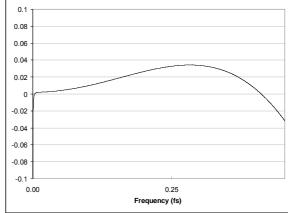

| INPUT SIGNAL PATH ANALOGUE TO DIGITAL CONVERTER (ADC) DIGITAL AUDIO PATHS THERMAL SENSING GENERAL PURPOSE INPUT/OUTPUT DIGITAL AUDIO INTERFACE DIGITAL AUDIO INTERFACE CONTROL CLOCKING AND SAMPLE RATES CONTROL INTERFACE POWER MANAGEMENT POWER DOMAINS REGISTER MAP REGISTER BITS BY ADDRESS DIGITAL FILTER CHARACTERISTICS ADC FILTER RESPONSES ADC HIGH PASS FILTER RESPONSES                                                                               | 36<br>39<br>40<br>41<br>56<br>63<br>67<br>75<br>79<br>82<br>82<br>97       |

| INPUT SIGNAL PATH ANALOGUE TO DIGITAL CONVERTER (ADC) DIGITAL AUDIO PATHS THERMAL SENSING GENERAL PURPOSE INPUT/OUTPUT DIGITAL AUDIO INTERFACE DIGITAL AUDIO INTERFACE CONTROL CLOCKING AND SAMPLE RATES. CONTROL INTERFACE POWER MANAGEMENT POWER DOMAINS REGISTER MAP REGISTER BITS BY ADDRESS DIGITAL FILTER CHARACTERISTICS ADC FILTER RESPONSES APPLICATIONS INFORMATION                                                                                    | 36<br>39<br>40<br>41<br>56<br>56<br>67<br>75<br>79<br>82<br>82<br>82<br>97 |

| INPUT SIGNAL PATH ANALOGUE TO DIGITAL CONVERTER (ADC) DIGITAL AUDIO PATHS THERMAL SENSING GENERAL PURPOSE INPUT/OUTPUT DIGITAL AUDIO INTERFACE DIGITAL AUDIO INTERFACE CONTROL CLOCKING AND SAMPLE RATES CONTROL INTERFACE POWER MANAGEMENT POWER DOMAINS REGISTER MAP REGISTER BITS BY ADDRESS DIGITAL FILTER CHARACTERISTICS ADC FILTER RESPONSES ADC HIGH PASS FILTER RESPONSES APPLICATIONS INFORMATION RECOMMENDED EXTERNAL COMPONENTS.                     | 36<br>39<br>40<br>41<br>56<br>63<br>75<br>75<br>82<br>82<br>82<br>97       |

| INPUT SIGNAL PATH ANALOGUE TO DIGITAL CONVERTER (ADC) DIGITAL AUDIO PATHS THERMAL SENSING GENERAL PURPOSE INPUT/OUTPUT DIGITAL AUDIO INTERFACE DIGITAL AUDIO INTERFACE CONTROL CLOCKING AND SAMPLE RATES CONTROL INTERFACE POWER MANAGEMENT POWER DOMAINS REGISTER MAP. REGISTER BITS BY ADDRESS DIGITAL FILTER CHARACTERISTICS ADC FILTER RESPONSES ADC HIGH PASS FILTER RESPONSES APPLICATIONS INFORMATION RECOMMENDED EXTERNAL COMPONENTS. PACKAGE DIMENSIONS | 36 36 36 40 41 56 63 75 82 82 82 97                                        |

| INPUT SIGNAL PATH ANALOGUE TO DIGITAL CONVERTER (ADC) DIGITAL AUDIO PATHS THERMAL SENSING GENERAL PURPOSE INPUT/OUTPUT DIGITAL AUDIO INTERFACE DIGITAL AUDIO INTERFACE CONTROL CLOCKING AND SAMPLE RATES CONTROL INTERFACE POWER MANAGEMENT POWER DOMAINS REGISTER MAP REGISTER BITS BY ADDRESS DIGITAL FILTER CHARACTERISTICS ADC FILTER RESPONSES ADC HIGH PASS FILTER RESPONSES APPLICATIONS INFORMATION RECOMMENDED EXTERNAL COMPONENTS.                     | 36 36 39 40 41 56 67 75 79 82 82 97 97                                     |

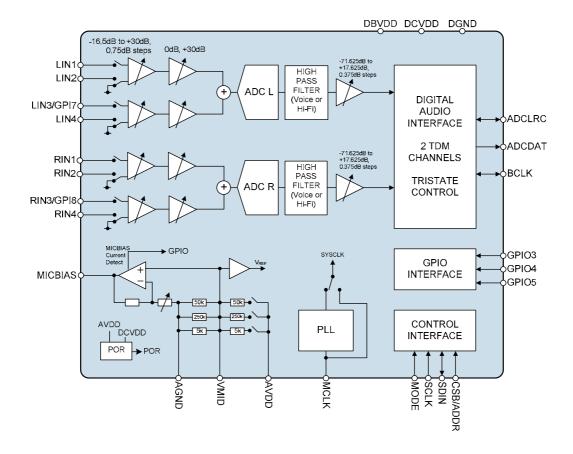

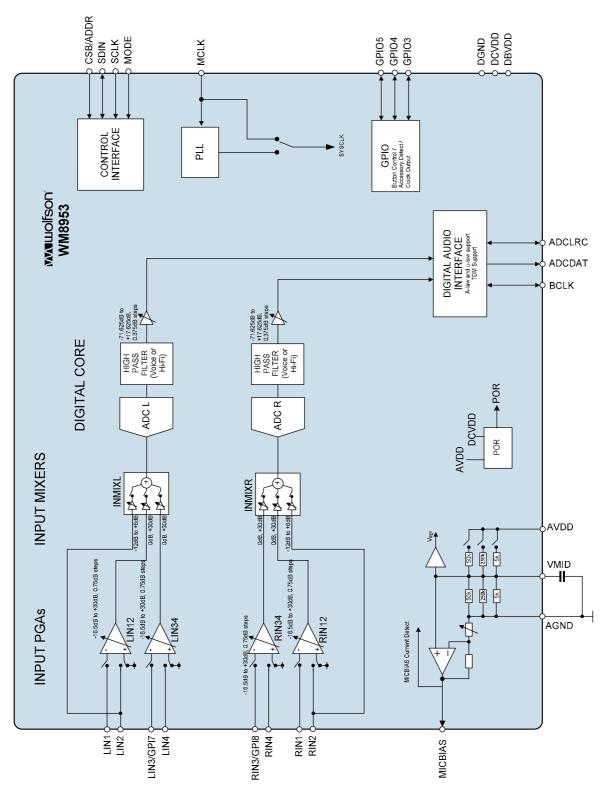

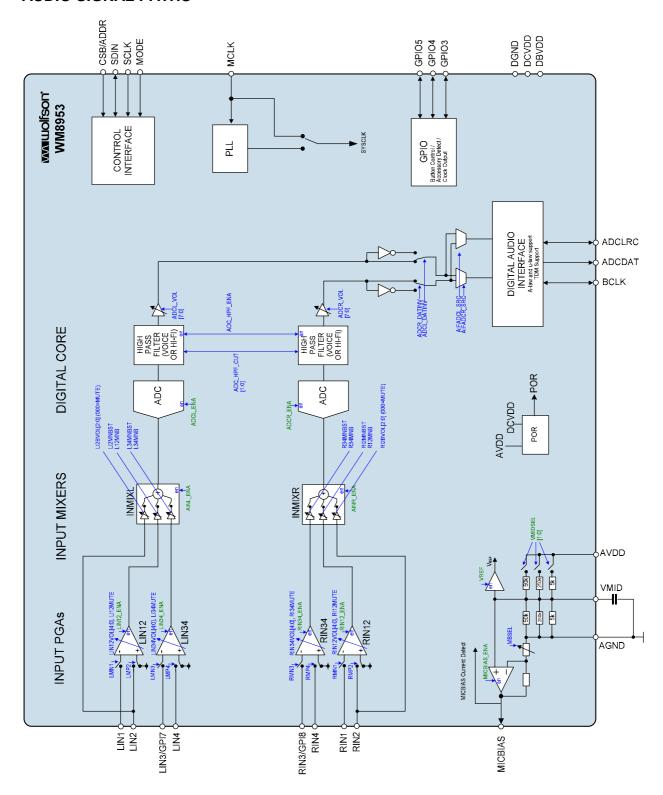

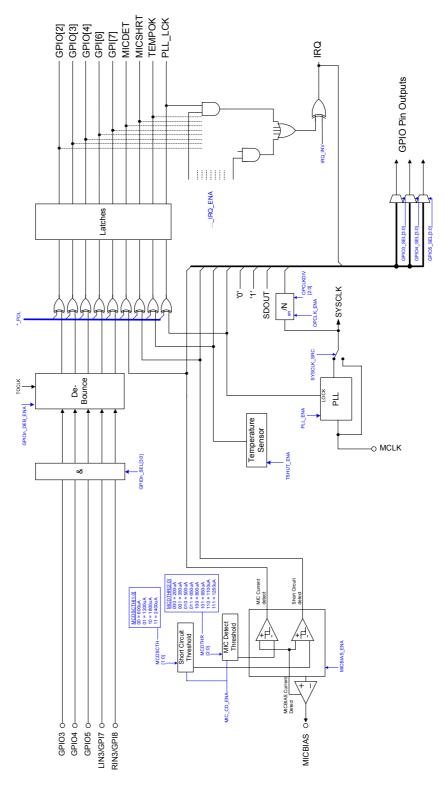

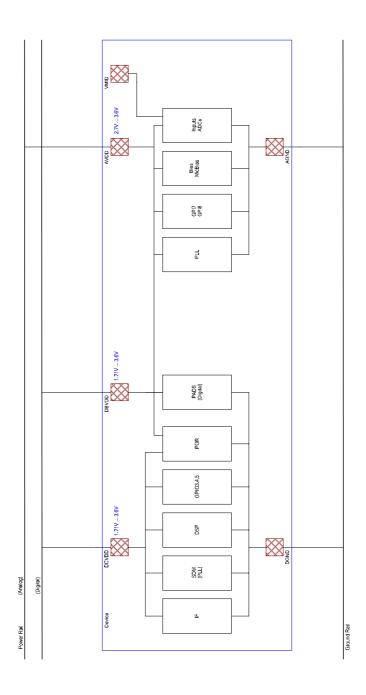

# **BLOCK DIAGRAM**

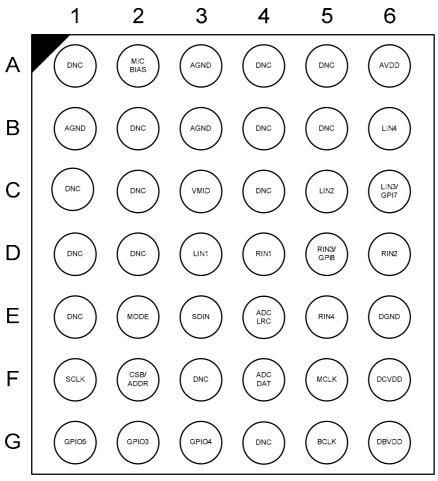

# **PIN CONFIGURATION**

**TOP VIEW**

# **ORDERING INFORMATION**

| ORDER CODE   | TEMPERATURE RANGE | PACKAGE                                   | MOISTURE<br>SENSITIVITY LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|--------------|-------------------|-------------------------------------------|-------------------------------|-------------------------------|

| WM8953ECS/RV | -40°C to +85°C    | 42-ball W-CSP<br>(Pb-free, Tape and reel) | MSL3                          | 260°C                         |

Note:

Reel quantity = 3500

# **PIN DESCRIPTION**

| PIN NO             | NAME        | TYPE                   | DESCRIPTION                                              |

|--------------------|-------------|------------------------|----------------------------------------------------------|

| A2                 | MICBIAS     | Analogue Output        | Microphone bias                                          |

| D3                 | LIN1        | Analogue Input         | Left channel single-ended MIC input /                    |

|                    |             |                        | Left channel negative differential MIC input             |

| C5                 | LIN2        | Analogue Input         | Left channel line input /                                |

|                    |             |                        | Left channel positive differential MIC input             |

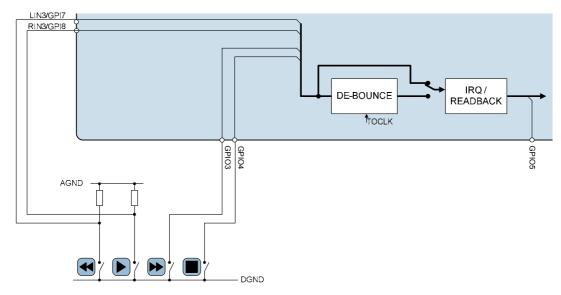

| C6                 | LIN3 / GPI7 | Analogue Input /       | Left channel line input /                                |

|                    |             | Digital Input          | Left channel negative differential MIC input /           |

|                    |             |                        | Accessory or button detect input pin                     |

| B6                 | LIN4        | Analogue Input         | Left channel line input /                                |

|                    |             |                        | Left channel positive differential MIC input /           |

| D4                 | RIN1        | Analogue Input         | Right channel single-ended MIC input /                   |

|                    |             |                        | Right channel negative differential MIC input            |

| D6                 | RIN2        | Analogue Input         | Right channel line input /                               |

|                    |             |                        | Right channel positive differential MIC input            |

| D5                 | RIN3 / GPI8 | Analogue Input /       | Right channel line input /                               |

|                    |             | Digital Input          | Right channel negative differential MIC input /          |

|                    |             |                        | Accessory or button detect input pin                     |

| E5                 | RIN4        | Analogue Input         | Left channel line input /                                |

|                    |             |                        | Left channel positive differential MIC input /           |

| F6                 | DCVDD       | Supply                 | Digital core supply                                      |

| E6                 | DGND        | Supply                 | Digital ground (Return path for both DCVDD and DBVDD)    |

| G6                 | DBVDD       | Supply                 | Digital buffer (I/O) supply                              |

| A6                 | AVDD        | Supply                 | Analogue supply                                          |

| A3, B1,<br>B3      | AGND        | Supply                 | Analogue ground (Return path for AVDD)                   |

| F5                 | MCLK        | Digital Input          | Master clock                                             |

| G5                 | BCLK        | Digital Input / Output | Audio interface bit clock                                |

| E4                 | ADCLRC      | Digital Input / Output | Audio interface ADC left / right clock                   |

| F4                 | ADCDAT      | Digital Output         | ADC digital audio data                                   |

| E2                 | MODE        | Digital Input          | Selects 2-wire or 3/4 -wire control                      |

| F2                 | CSB / ADDR  | Digital Input          | 3/4 -wire chip select or 2-wire address select           |

| F1                 | SCLK        | Digital Input          | Control interface clock input                            |

| E3                 | SDIN        | Digital Input / Output | Control interface data input / 2-wire acknowledge output |

| C3                 | VMID        | Analogue Output        | Midrail voltage decoupling capacitor                     |

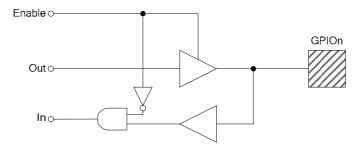

| G2                 | GPIO3       | Digital Input / Output | GPIO pin                                                 |

| G3                 | GPIO4       | Digital Input / Output | GPIO pin                                                 |

| G1                 | GPIO5       | Digital Input / Output | GPIO pin                                                 |

| A1, A4,            | DNC         | Do Not Connect         |                                                          |

| A5, B2,            |             |                        |                                                          |

| B4, B5,<br>C1, C2, |             |                        |                                                          |

| C1, C2,<br>C4, D1, |             |                        |                                                          |

| D2, E1,            |             |                        |                                                          |

| F3, G4             |             |                        |                                                          |

### **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at  $<30^{\circ}C$  / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                                   | MIN        | MAX         |

|---------------------------------------------|------------|-------------|

| Supply voltages                             | -0.3V      | +4.5V       |

| Voltage range digital inputs                | DGND -0.3V | DBVDD +0.3V |

| Voltage range analogue inputs               | AGND -0.3V | AVDD +0.3V  |

| Operating temperature range, T <sub>A</sub> | -40°C      | +85°C       |

| Junction temperature, T <sub>JMAX</sub>     | -40°C      | +150°C      |

| Storage temperature after soldering         | -65°C      | +150°C      |

### RECOMMENDED OPERATING CONDITIONS

| PARAMETER                     | SYMBOL     | MIN  | TYP | MAX | UNIT |

|-------------------------------|------------|------|-----|-----|------|

| Digital supply range (Core)   | DCVDD      | 1.71 |     | 3.6 | V    |

| Digital supply range (Buffer) | DBVDD      | 1.71 |     | 3.6 | V    |

| Analogue supply range         | AVDD       | 2.7  |     | 3.6 | V    |

| Ground                        | DGND, AGND |      | 0   |     | V    |

## Notes

- 1. Analogue and digital grounds must always be within 0.3V of each other.

- 2. All digital and analogue supplies are completely independent from each other (i.e. not internally connected).

- 3. DCVDD must be less than or equal to AVDD.

- 4. DCVDD must be less than or equal to DBVDD.

## THERMAL PERFORMANCE

Thermal analysis should be performed in the intended application to prevent the WM8953 from exceeding maximum junction temperature. Several contributing factors affect thermal performance most notably the physical properties of the mechanical enclosure, location of the device on the PCB in relation to surrounding components and the number of PCB layers. Connecting the GND balls through thermal vias and into a large ground plane will aid heat extraction.

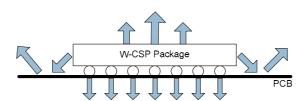

Three main heat transfer paths exist to surrounding air as illustrated below in Figure 1:

- Package top to air (radiation).

- Package bottom to PCB (radiation).

- Package balls to PCB (conduction).

Figure 1 Heat Transfer Paths

The temperature rise  $T_R$  is given by  $T_R = P_D * \Theta_{JA}$

- P<sub>D</sub> is the power dissipated in the device.

- $\Theta_{JA}$  is the thermal resistance from the junction of the die to the ambient temperature and is therefore a measure of heat transfer from the die to surrounding air.  $\Theta_{JA}$  is determined with reference to JEDEC standard JESD51-9.

The junction temperature  $T_J$  is given by  $T_J = T_A + T_R$ , where  $T_A$  is the ambient temperature.

| PARAMETER                      | SYMBOL         | MIN | TYP | MAX | UNIT |

|--------------------------------|----------------|-----|-----|-----|------|

| Operating temperature range    | T <sub>A</sub> | -40 |     | 85  | °C   |

| Operating junction temperature | TJ             | -40 |     | 100 | °C   |

| Thermal Resistance             | $\Theta_{JA}$  |     | 43  |     | °C/W |

# **ELECTRICAL CHARACTERISTICS**

### **Test Conditions**

DCVDD = 1.8V, DBVDD = 3.3V, AVDD = 3.3V,  $T_A$  = +25°C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                                                                 | TEST                                                                                                           | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MIN | TYP      | MAX | UNIT        |  |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----|-------------|--|

| Analogue Input Pin Maximum Signal Levels (LIN1, LIN2, LIN3, LIN4, RIN1, RIN2, RIN3, RIN4) |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |          |     |             |  |

| Maximum Full-Scale PGA<br>Input Signal Level<br>Note 1; Note 2; Note 3                    | Single-ended PGA<br>input on LIN1, LIN3,<br>RIN1 or RIN3, output<br>to INMIXL or INMIXR                        | LINI LINE ON THE ONE OF THE ONE O |     | 1.0<br>0 |     | Vrms<br>dBV |  |

| 1,166 2,166 2                                                                             | Differential PGA input<br>on LIN1/LIN2,<br>LIN3/LIN4, RIN1/RIN2<br>or RIN3/RIN4, output<br>to INMIXL or INMIXR | LINI, LING, RRH of RRD  ODB  URC JUNG LING LING LING LING A OF RINS4  LING A OF RINS4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 1.0<br>0 |     | Vrms<br>dBV |  |

| Maximum Full-Scale Line<br>Input Signal Level<br>Note 1; Note 2; Note 3                   | Line input on LIN2,<br>LIN4, RIN2 or RIN4 to<br>INMIXL or INMIXR                                               | LIN2, LIN4,<br>RIN2 or<br>RIN4 INMIXL or INMIXR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 1.0      |     | Vrms<br>dBV |  |

#### Notes

- 1. Maximum full scale signal changes in proportion to AVDD (AVDD/3.3).

- 2. When mixing input PGA outputs and line inputs, the total signal must not exceed 1Vrms (0dBV).

- 3. A 1.0Vrms differential signal equates to 0.5Vrms/-6dBV per input.

### **Test Conditions**

DCVDD = 1.8V, DBVDD = 3.3V, AVDD = 3.3V,  $T_A$  = +25°C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                    | TEST C                    | ONDITIONS                       | MIN | TYP | MAX | UNIT      |

|----------------------------------------------|---------------------------|---------------------------------|-----|-----|-----|-----------|

| Analogue Input Pin Impe                      |                           |                                 |     |     |     |           |

| PGA Input Resistance                         | LIN1, LIN3, RIN1 or RIN3  |                                 |     |     | kΩ  |           |

|                                              | (PGA Gain = -16.5dB)      | R <sub>IN</sub>                 |     |     |     |           |

| Note: this will be seen in                   | LIN1, LIN3, RIN1 or RIN3  | LIN1, LIN3,<br>RIN1 or RIN3     |     | 33  |     | $k\Omega$ |

| parallel with the resistance of other        | (PGA Gain = 0dB)          | LIN12, LIN13,<br>RIN12 or RIN34 |     |     |     |           |

| enabled input paths                          | LIN1, LIN3, RIN1 or RIN3  |                                 |     | 2   |     | $k\Omega$ |

| from the same pin                            | (PGA Gain = +30dB)        |                                 |     |     |     |           |

|                                              | LIN2, LIN4, RIN2 or RIN4  | LIN2, LIN4,                     |     | 65  |     | $k\Omega$ |

|                                              | (Constant for all gains)  | RIN2 or RIN4                    |     |     |     |           |

|                                              |                           | LIN12, LIN13,<br>RIN12 or RIN34 |     |     |     |           |

| Line Input Resistance                        | LIN2 or RIN2 to INMIXL or | LIN2 or                         |     | 60  |     | kΩ        |

|                                              | INMIXR (-12dB)            | RIN2 RIN                        |     |     |     |           |

| Note: this will be seen in parallel with the |                           |                                 | 15  |     | kΩ  |           |

| resistance of other                          | LIN2 or RIN2 to INMIXL or | INMIXL or INMIXR                |     | 7.5 |     | kΩ        |

| enabled input paths from the same pin        | INMIXR (+6dB)             |                                 |     |     |     |           |

| Input Capacitance                            | All analogue input pins   |                                 |     | 10  |     | pF        |

### **Test Conditions**

DCVDD = 1.8V, DBVDD = 3.3V, AVDD = 3.3V,  $T_A$  = +25°C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                                               | TEST CONDITIONS                                 | MIN | TYP   | MAX | UNIT |  |

|-------------------------------------------------------------------------|-------------------------------------------------|-----|-------|-----|------|--|

| Input Programmable Gain Amplifiers (PGAs) LIN12, LIN34, RIN12 and RIN34 |                                                 |     |       |     |      |  |

| Minimum Programmable Gain                                               |                                                 |     | -16.5 |     | dB   |  |

| Maximum Programmable Gain                                               |                                                 |     | 30    |     | dB   |  |

| Programmable Gain Step Size                                             | Guaranteed monotonic                            |     | 1.5   |     | dB   |  |

| Mute Attenuation                                                        | Inputs disconnected                             |     | 90    |     | dB   |  |

| Common Mode Rejection Ratio                                             | Single PGA in differential mode, gain = +30dB   |     | 60    |     | dB   |  |

| (1kHz input)                                                            | Single PGA in differential mode, gain = 0dB     |     | 50    |     |      |  |

|                                                                         | Single PGA in differential mode, gain = -16.5dB |     | 50    |     |      |  |

| Input Mixers INMIXL and INMIXR                                          |                                                 |     |       |     |      |  |

| Minimum Programmable Gain                                               | PGA Outputs to INMIXL and INMIXR                |     | 0     |     | dB   |  |

| Maximum Programmable Gain                                               | PGA Outputs to INMIXL and INMIXR                |     | +30   |     | dB   |  |

| Programmable Gain Step Size                                             | PGA Outputs to INMIXL and INMIXR                |     | 30    |     | dB   |  |

| Minimum Programmable Gain                                               | Line Inputs to INMIXL and INMIXR                |     | -12   |     | dB   |  |

| Maximum Programmable Gain                                               | Line Inputs to INMIXL and INMIXR                |     | +6    |     | dB   |  |

| Programmable Gain Step Size                                             | Line Inputs to INMIXL and INMIXR                |     | 3     |     | dB   |  |

| Mute attenuation                                                        |                                                 |     | 95    |     | dB   |  |

## **Test Conditions**

DCVDD = 1.8V, DBVDD = 3.3V, AVDD = 3.3V,  $T_A$  = +25°C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER              |                            | TEST CONDITIONS                                         | MIN | TYP  | MAX | UNIT |

|------------------------|----------------------------|---------------------------------------------------------|-----|------|-----|------|

| ADC Input Path Perform | ance                       |                                                         |     |      |     |      |

| SNR (A-weighted)       | Line inputs to             |                                                         | 84  | 94   |     | dB   |

| THD (-1dBFS input)     | ADC via INMIXL             |                                                         |     | -84  | -75 | dB   |

| THD+N (-1dBFS input)   | and INMIXR,<br>AVDD = 3.3V | L2or                                                    |     | -82  | -73 | dB   |

| Crosstalk (L/R)        | 7.700                      | RI2 ADC I                                               |     | -100 |     | dB   |

| AVDD PSRR (217Hz)      |                            | + or ADCR                                               |     | 45   |     | dB   |

| DCVDD PSRR (217Hz)     |                            | INMIXL or INMIXR                                        |     | 80   |     | dB   |

| SNR (A-weighted)       | Line inputs to             |                                                         |     | 93   |     | dB   |

| THD (-1dBFS input)     | ADC via INMIXL             |                                                         |     | -78  |     | dB   |

| THD+N (-1dBFS input)   | and INMIXR,<br>AVDD = 2.7V |                                                         |     | -76  |     | dB   |

| SNR (A-weighted)       | Input PGAs to              |                                                         | 84  | 94   |     | dB   |

| THD (-1dBFS input)     | ADC via INMIXL             | LIN1, LIN3, OdB INMIXL or                               |     | -84  | -75 | dB   |

| THD+N (-1dBFS input)   | or INMIXR,<br>AVDD = 3.3V  | INMIXR ADCL or                                          |     | -82  | -73 | dB   |

| Crosstalk (L/R)        |                            | + ADCR                                                  |     | -100 |     | dB   |

| AVDD PSRR (217Hz)      |                            | LIN2, LIN4, / LIN12, LIN34, RIN2 or RIN4 RIN12 or RIN34 |     | 45   |     | dB   |

| SNR (A-weighted)       | Input PGAs to              | (Single-ended or<br>differential mode)                  |     | 92   |     | dB   |

| THD (-1dBFS input)     | ADC via INMIXL             |                                                         |     | -78  |     | dB   |

| THD+N (-1dBFS input)   | or INMIXR,<br>AVDD = 2.7V  |                                                         |     | -76  |     | dB   |

## **Test Conditions**

DCVDD = 1.8V, DBVDD = 3.3V, AVDD = 3.3V,  $T_A$  = +25°C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                             | TEST CONDITIONS             | MIN                                   | TYP       | MAX                                   | UNIT   |

|-------------------------------------------------------|-----------------------------|---------------------------------------|-----------|---------------------------------------|--------|

| Analogue Reference Levels                             |                             |                                       |           |                                       |        |

| VMID Midrail Reference Voltage                        |                             | -3%                                   | AVDD/2    | +3%                                   | V      |

| Microphone Bias                                       | •                           | •                                     |           |                                       | •      |

| Bias Voltage                                          | 3mA load current            | -5%                                   | 0.9×AVDD  | +5%                                   | V      |

|                                                       | MBSEL=0                     |                                       |           |                                       |        |

|                                                       | 3mA load current            | -5%                                   | 0.65×AVDD | +5%                                   | V      |

|                                                       | MBSEL=1                     |                                       |           |                                       |        |

| Bias Current Source                                   |                             |                                       |           | 3                                     | mA     |

| Output Noise Density                                  | 1kHz to 20kHz               |                                       | 100       |                                       | nV/√Hz |

| AVDD PSRR (217Hz)                                     | 100mV pk-pk @217Hz          |                                       | 45        |                                       | dB     |

| ,                                                     | on AVDD                     |                                       |           |                                       |        |

| Digital Input / Output                                | -1                          | I.                                    |           | I                                     | I      |

| Input HIGH Level                                      |                             | 0.7×DBVDD                             |           |                                       | V      |

| Input LOW Level                                       |                             |                                       |           | 0.3×DBVDD                             | V      |

| Note that digital input pins should not be le         | eft unconnected / floating. | I                                     |           | 10.0                                  | I      |

| Internal pull-up/pull-down resistors may be           | •                           | GPIO5 if require                      | d.        |                                       |        |

| Output HIGH Level                                     | I <sub>OL</sub> =1mA        | 0.9×DBVDD                             |           |                                       | V      |

| Output LOW Level                                      | I <sub>OH</sub> =-1mA       | 0.07.22.722                           |           | 0.1×DBVDD                             | V      |

| Input capacitance                                     | ion iiii                    |                                       | 10        | 0                                     | pF     |

| Input leakage                                         |                             | -0.9                                  |           | 0.9                                   | uA     |

| PLL                                                   | _ <b>_</b>                  | 0.0                                   |           | 0.0                                   | u, t   |

| Input Frequency                                       | PRESCALE = 0b               | 7.7                                   |           | 18                                    | MHz    |

| input i requeitoy                                     | PRESCALE = 1b               | 14.4                                  |           | 36                                    | MHz    |

| Lock time                                             | TRESCALE - 10               | 14.4                                  | 200       | 30                                    | us     |

| GPIO                                                  |                             |                                       | 200       |                                       | us     |

|                                                       | SYSCLK=MCLK;                | 35                                    | 1         | 65                                    | %      |

| Clock output duty cycle (Integer OPCLKDIV)            | OPCLKDIV=0000               | 33                                    |           | 05                                    | /0     |

| (integer OF CERDIV)                                   | SYSCLK=MCLK;                | 45                                    |           | 55                                    | %      |

|                                                       | OPCLKDIV=1000               | 45                                    |           | 55                                    | 70     |

|                                                       | SYSCLK=PLL output;          | 45                                    |           | 55                                    | %      |

|                                                       | OPCLKDIV=0000               | 45                                    |           | 55                                    | 70     |

|                                                       |                             | 45                                    |           |                                       | %      |

|                                                       | SYSCLK=PLL output;          | 45                                    |           | 55                                    | 70     |

| Clock output duty cycle                               | OPCLKDIV=1000               | 22                                    |           | 00                                    | %      |

|                                                       | SYSCLK=MCLK;                | 33                                    |           | 66                                    | %      |

| (Non-integer OPCLKDIV)                                | OPCLKDIV=0100               | 20                                    |           | 60                                    | 0/     |

|                                                       | SYSCLK=PLL output;          | 33                                    |           | 66                                    | %      |

| Intermed an arrange time for a constant               | OPCLKDIV=0100               | 021 / 5                               |           | 022 / 5                               |        |

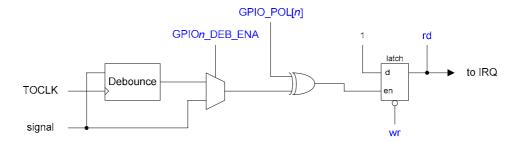

| Interrupt response time for accessory / button detect | Input de-bounced            | 2 <sup>21</sup> / f <sub>SYSCLK</sub> |           | 2 <sup>22</sup> / f <sub>SYSCLK</sub> | S      |

| Dation doloot                                         | Input de-bounced            | 2 <sup>19</sup> / f <sub>SYSCLK</sub> |           | 2 <sup>20</sup> / f <sub>SYSCLK</sub> | s      |

|                                                       | TOCLKSEL=1                  |                                       |           |                                       |        |

|                                                       | Input not de-bounced        |                                       | 0         |                                       | S      |

#### **TERMINOLOGY**

1. Signal-to-Noise Ratio (dB) – SNR is a measure of the difference in level between the maximum theoretical full scale output signal and the output with no input signal applied.

- 2. Total Harmonic Distortion (dB) THD is the level of the rms value of the sum of harmonic distortion products relative to the amplitude of the measured output signal.

- 3. Total Harmonic Distortion plus Noise (dB) THD+N is the level of the rms value of the sum of harmonic distortion products plus noise in the specified bandwidth relative to the amplitude of the measured output signal.

- 4. Crosstalk (L/R) (dB) left-to-right and right-to-left channel crosstalk is the measured signal level in the idle channel at the test signal frequency relative to the signal level at the output of the active channel. The active channel is configured and supplied with an appropriate input signal to drive a full scale output, with signal measured at the output of the associated idle channel. For example, measured signal level on the output of the idle right channel (RIN2 to ADCR) with a full scale signal level at the output of the active left channel (LIN1 to ADCL).

- 5. Multi-Path Channel Separation (dB) is the measured signal level in the idle path at the test signal frequency relative to the signal level at the output of the active path. The active path is configured and supplied with an appropriate input signal to drive a full scale output, with signal measured at the output of the specified idle path.

- 6. All performance measurements carried out with 20kHz low pass filter, and where noted an A-weighted filter. Failure to use such a filter will result in higher THD and lower SNR readings than are found in the Electrical Characteristics. The low pass filter removes out of band noise; although it is not audible it may affect dynamic specification values.

- 7. Mute Attenuation This is a measure of the difference in level between the full scale output signal and the output with mute applied.

# **TYPICAL POWER CONSUMPTION**

| Mode                                          | Other settings |     |     |     | IAVDD | IDBVDD | IDCVDD | Total Power |

|-----------------------------------------------|----------------|-----|-----|-----|-------|--------|--------|-------------|

|                                               | Other settings | (V) | (V) | (V) | (mA)  | (mA)   | (mA)   | (mW)        |

| Standby/Sleep                                 |                |     |     |     |       |        |        |             |

|                                               |                | 2.7 | 1.8 | 1.8 | 0.028 | 0.000  | 0.000  | 0.075       |

| OFF (default state at power-up)               | No Clocks      | 3.0 | 2.5 | 2.5 | 0.029 | 0.000  | 0.000  | 0.087       |

| or (default state at power-up)                | NO CIOCKS      | 3.3 | 3.3 | 3.3 | 0.030 | 0.000  | 0.000  | 0.099       |

|                                               |                | 3.6 | 3.6 | 3.6 | 0.031 | 0.000  | 0.000  | 0.114       |

|                                               |                | 2.7 | 1.8 | 1.8 | 0.008 | 0.000  | 0.000  | 0.020       |

| OFF (thermal sensor disabled)                 | No Clocks      | 3.0 | 2.5 | 2.5 | 0.008 | 0.000  | 0.000  | 0.024       |

| OTT (ITETHIAL SELISOL UISABIEU)               | NO CIOCKS      | 3.3 | 3.3 | 3.3 | 0.009 | 0.000  | 0.000  | 0.029       |

|                                               |                | 3.6 | 3.6 | 3.6 | 0.009 | 0.000  | 0.000  | 0.035       |

|                                               | With Clocks    | 2.7 | 1.8 | 1.8 | 0.087 | 0.004  | 0.459  | 1.068       |

| SLEEP (VMID enabled, thermal sensor anabled)  |                | 3.0 | 2.5 | 2.5 | 0.096 | 0.008  | 0.694  | 2.044       |

| OLLET (VIIII) CHASICO, MCMIAI SCHSOI ANASICO) |                | 3.3 | 3.3 | 3.3 | 0.106 | 0.014  | 1.025  | 3.780       |

|                                               |                | 3.6 | 3.6 | 3.6 | 0.117 | 0.017  | 1.162  | 4.667       |

| ADC Record                                    |                |     |     |     |       |        |        |             |

|                                               |                | 2.7 | 1.8 | 1.8 | 5.272 | 0.023  | 2.285  | 18.389      |

| Stereo Line Record                            | fs=44.1kHz     | 3.0 | 2.5 | 2.5 | 5.603 | 0.039  | 3.317  | 25.199      |

| (L/RIN2 to INMIXL/R bypassing PGA)            | 15-44. IKHZ    | 3.3 | 3.3 | 3.3 | 5.927 | 0.060  | 4.728  | 35.358      |

|                                               |                | 3.6 | 3.6 | 3.6 | 6.261 | 0.063  | 5.295  | 41.830      |

|                                               |                | 2.7 | 1.8 | 1.8 | 5.125 | 0.017  | 0.758  | 15.233      |

| Stereo Line Record                            | fs=8kHz        | 3.0 | 2.5 | 2.5 | 5.434 | 0.027  | 1.123  | 19.177      |

| (L/RIN2 to INMIXL/R bypassing PGA)            | 19-0VI IZ      | 3.3 | 3.3 | 3.3 | 5.738 | 0.061  | 1.634  | 24.528      |

|                                               |                | 3.6 | 3.6 | 3.6 | 6.053 | 0.062  | 1.841  | 28.642      |

### Notes:

- 1. All figures are quoted at  $T_A = +25$ °C

- 2. All figures are quoted as quiescent current unless otherwise stated.

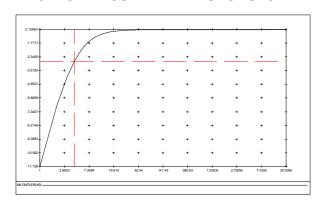

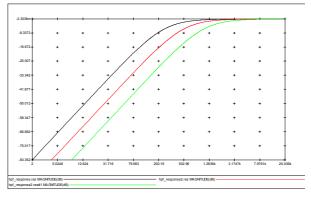

# **PSRR PERFORMANCE**

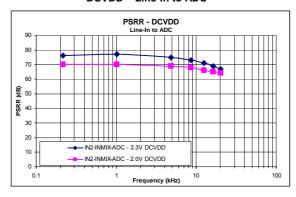

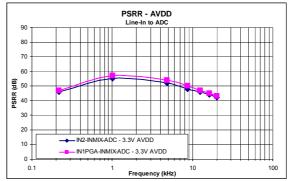

DCVDD - Line-In to ADC

AVDD - Line-In to ADC

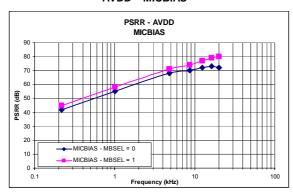

AVDD - MICBIAS

Note: All figures based on 100mVp-p injected on the supply at the relevant test frequency.

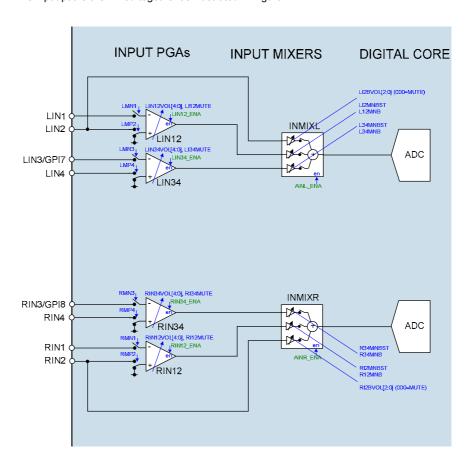

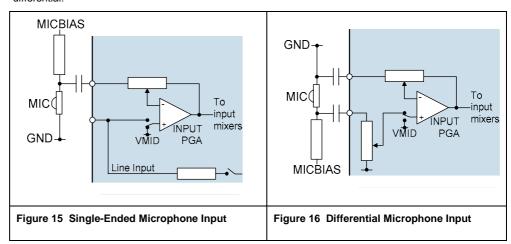

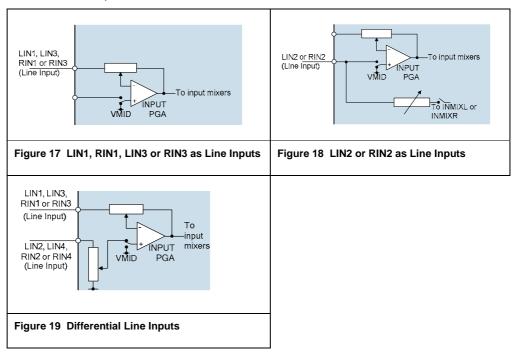

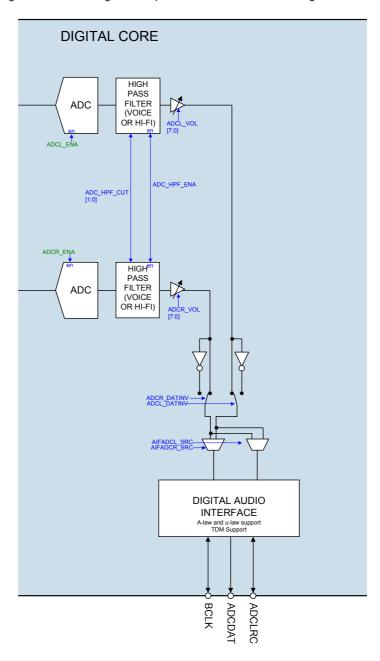

# **AUDIO SIGNAL PATHS**

# **SIGNAL TIMING REQUIREMENTS**

# **SYSTEM CLOCK TIMING**

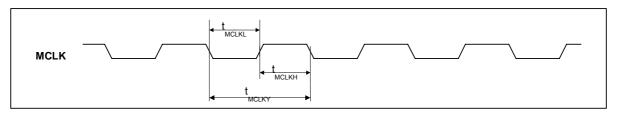

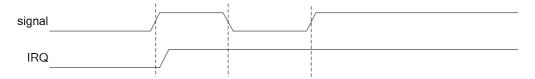

Figure 2 System Clock Timing Requirements

## **Test Conditions**

DCVDD=1.8V, DBVDD=AVDD=3.3V, DGND=AGND=0V, T<sub>A</sub> = +25°C

| PARAMETER                       | SYMBOL             | CONDITIONS                               | MIN   | TYP | MAX   | UNIT |

|---------------------------------|--------------------|------------------------------------------|-------|-----|-------|------|

| System Clock Timing Information |                    |                                          |       |     |       |      |

| MCLK cycle time                 | T <sub>MCLKY</sub> |                                          | 33.33 |     |       | ns   |

| MCLK duty cycle                 |                    | = T <sub>MCLKH</sub> /T <sub>MCLKL</sub> | 60:40 |     | 40:60 |      |

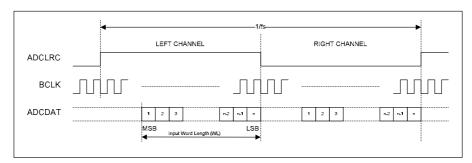

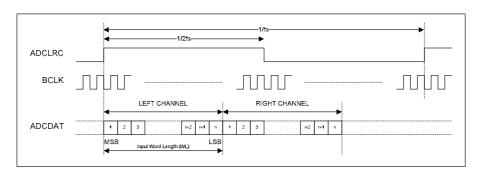

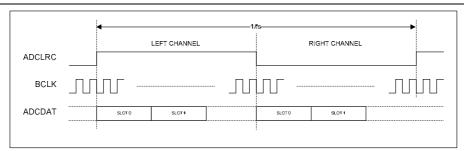

# **AUDIO INTERFACE TIMING - MASTER MODE**

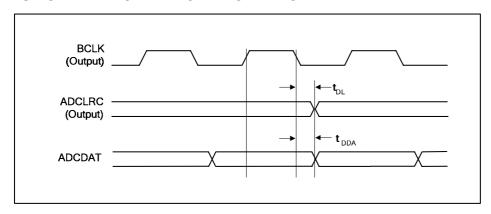

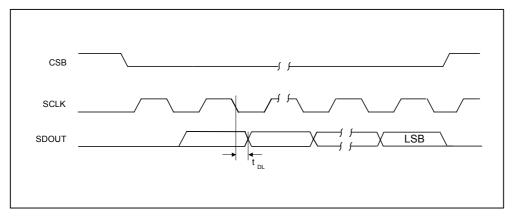

Figure 3 Digital Audio Data Timing - Master Mode (see Control Interface)

### **Test Conditions**

DCVDD=1.8V, DBVDD=AVDD=3.3V, DGND=AGND=0V,  $T_A$ =+25°C, Master Mode, fs=48kHz, MCLK=256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                       | SYMBOL           | MIN | TYP | MAX | UNIT |

|-------------------------------------------------|------------------|-----|-----|-----|------|

| Audio Data Timing Information                   |                  |     |     |     |      |

| ADCLRC propagation delay from BCLK falling edge | t <sub>DL</sub>  |     |     | 20  | ns   |

| ADCDAT propagation delay from BCLK falling edge | t <sub>DDA</sub> |     |     | 20  | ns   |

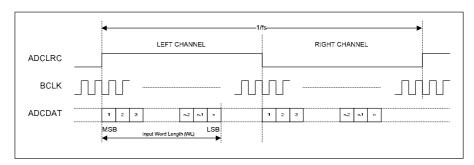

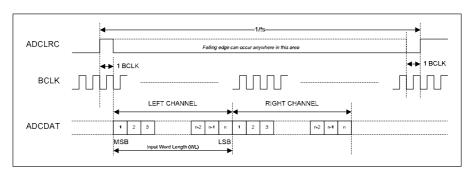

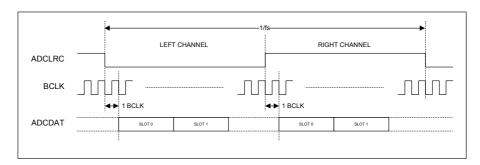

# **AUDIO INTERFACE TIMING - SLAVE MODE**

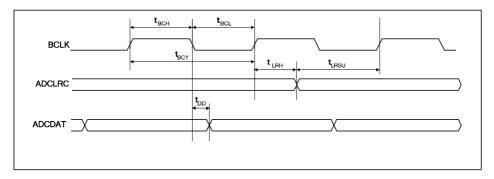

Figure 4 Digital Audio Data Timing - Slave Mode

### **Test Conditions**

DCVDD=1.8V, DBVDD=AVDD=3.3V, DGND=AGND=0V,  $T_A$ =+25°C, Slave Mode, fs=48kHz, MCLK=256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                       | SYMBOL            | MIN | TYP | MAX | UNIT |

|-------------------------------------------------|-------------------|-----|-----|-----|------|

| Audio Data Input Timing Information             |                   |     |     |     |      |

| BCLK cycle time                                 | t <sub>BCY</sub>  | 50  |     |     | ns   |

| BCLK pulse width high                           | t <sub>BCH</sub>  | 20  |     |     | ns   |

| BCLK pulse width low                            | t <sub>BCL</sub>  | 20  |     |     | ns   |

| ADCLRC set-up time to BCLK rising edge          | t <sub>LRSU</sub> | 20  |     |     | ns   |

| ADCLRC hold time from rising edge               | t <sub>LRH</sub>  | 10  |     |     | ns   |

| ADCDAT propagation delay from BCLK falling edge | t <sub>DD</sub>   |     |     | 20  | ns   |

# Note:

BCLK period should always be greater than or equal to MCLK period.

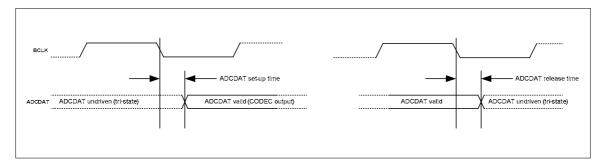

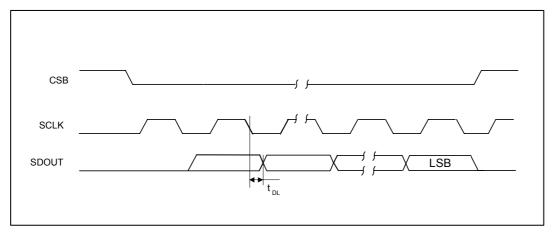

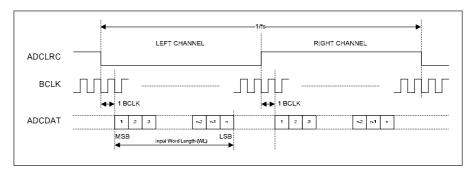

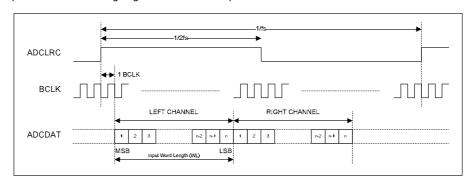

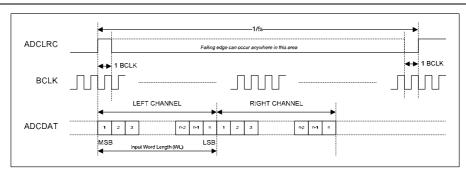

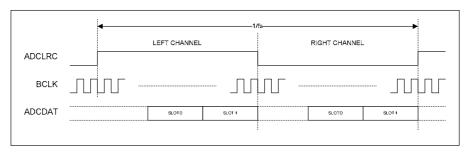

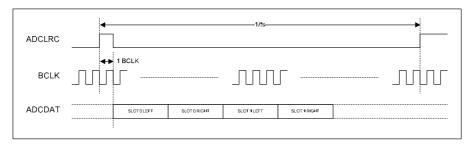

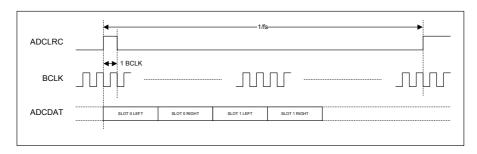

## **AUDIO INTERFACE TIMING - TDM MODE**

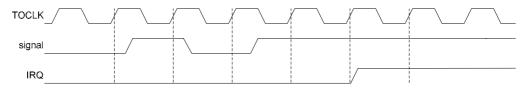

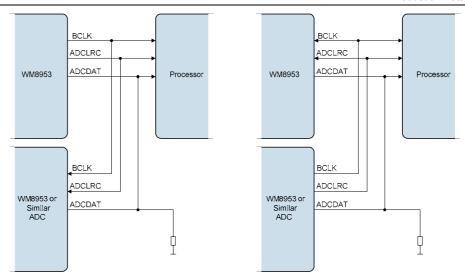

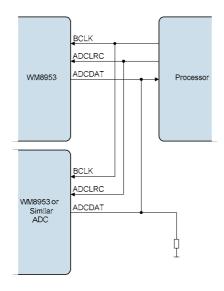

In TDM mode, it is important that two ADC devices to not attempt to drive the ADCDAT pin simultaneously. The timing of the WM8953 ADCDAT tri-stating at the start and end of the data transmission is described in Figure 5 and the table below.

Figure 5 Digital Audio Data Timing - TDM Mode

### **Test Conditions**

AVDD=3.3V, DGND=AGND=0V,  $T_A$ =+25°C, Master Mode, fs=48kHz, MCLK=256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                  | CONDITIONS               | MIN | TYP | MAX | UNIT |

|--------------------------------------------|--------------------------|-----|-----|-----|------|

| Audio Data Timing Information              |                          |     |     |     |      |

| ADCDAT setup time from BCLK falling edge   | DCVDD =<br>DBVDD = 3.6V  |     | 5   |     | ns   |

|                                            | DCVDD =<br>DBVDD = 1.71V |     | 15  |     | ns   |

| ADCDAT release time from BCLK falling edge | DCVDD =<br>DBVDD = 3.6V  |     | 5   |     | ns   |

|                                            | DCVDD =<br>DBVDD = 1.71V |     | 15  |     | ns   |

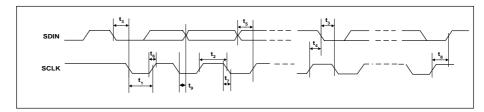

## **CONTROL INTERFACE TIMING – 2-WIRE MODE**

2-wire mode is selected by connecting the MODE pin low.

Figure 6 Control Interface Timing – 2-Wire Serial Control Mode

### **Test Conditions**

DCVDD=1.8V, DBVDD=AVDD=3.3V, DGND=AGND=0V,  $T_A$ =+25°C, Slave Mode, fs=48kHz, MCLK = 256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                     | SYMBOL          | MIN | TYP | MAX | UNIT |  |  |

|-----------------------------------------------|-----------------|-----|-----|-----|------|--|--|

| Program Register Input Information            |                 |     |     |     |      |  |  |

| SCLK Frequency                                |                 |     |     | 526 | kHz  |  |  |

| SCLK Low Pulse-Width                          | t <sub>1</sub>  | 1.3 |     |     | us   |  |  |

| SCLK High Pulse-Width                         | t <sub>2</sub>  | 600 |     |     | ns   |  |  |

| Hold Time (Start Condition)                   | t <sub>3</sub>  | 600 |     |     | ns   |  |  |

| Setup Time (Start Condition)                  | t <sub>4</sub>  | 600 |     |     | ns   |  |  |

| Data Setup Time                               | t <sub>5</sub>  | 100 |     |     | ns   |  |  |

| SDIN, SCLK Rise Time                          | t <sub>6</sub>  |     |     | 300 | ns   |  |  |

| SDIN, SCLK Fall Time                          | t <sub>7</sub>  |     |     | 300 | ns   |  |  |

| Setup Time (Stop Condition)                   | t <sub>8</sub>  | 600 |     |     | ns   |  |  |

| Data Hold Time                                | t <sub>9</sub>  |     |     | 900 | ns   |  |  |

| Pulse width of spikes that will be suppressed | t <sub>ps</sub> | 0   |     | 5   | ns   |  |  |

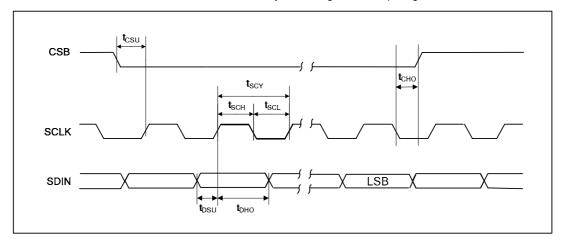

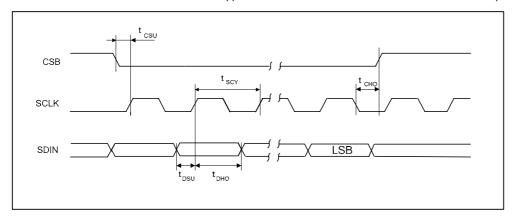

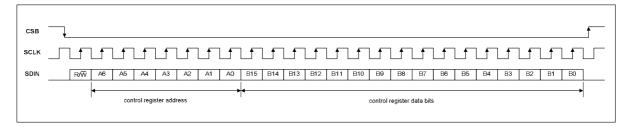

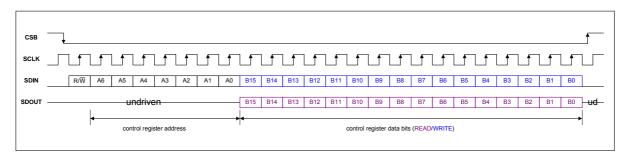

## **CONTROL INTERFACE TIMING – 3-WIRE MODE**

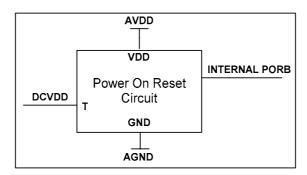

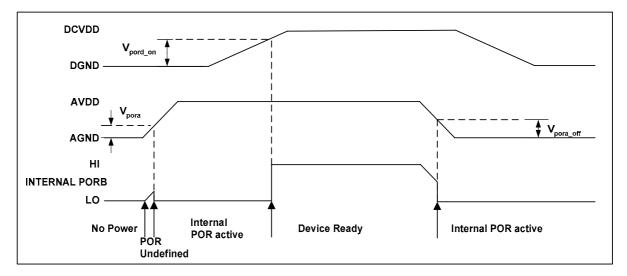

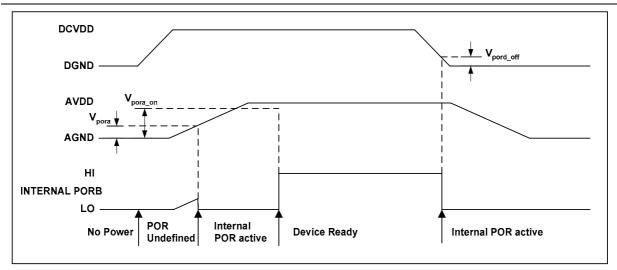

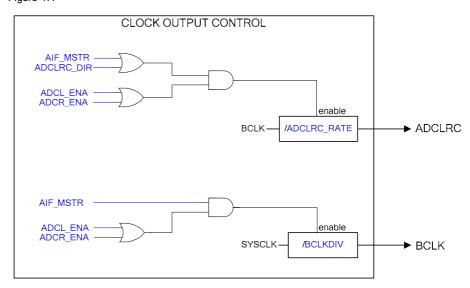

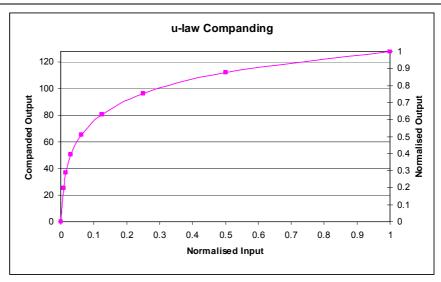

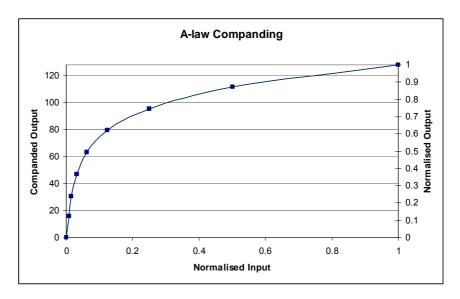

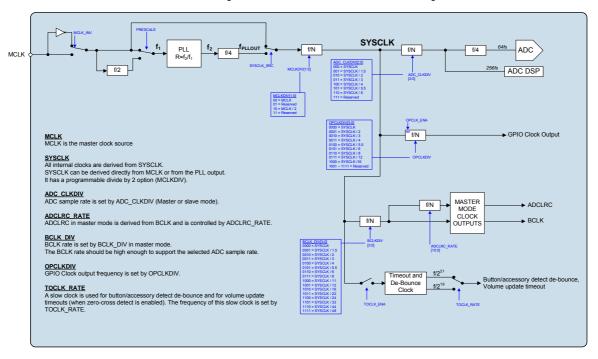

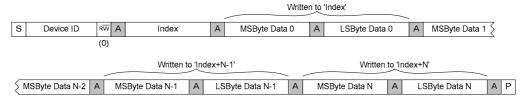

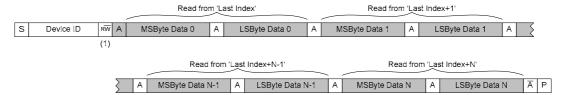

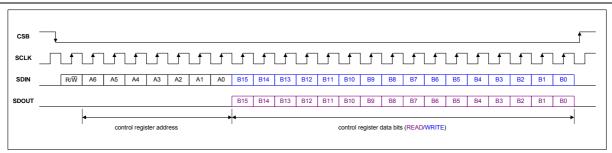

3-wire mode is selected by connecting the MODE pin high.